E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

# Advances in Wafer Probing with Ultra-Short Pitch SoCs

### Sriharsha Vinjamury

Principal Engineer, ARM Inc

#### **Abstract**

The semiconductor industry is in a constant state of evolution, driven by the relentless pursuit of improved performance, enhanced efficiency, and the ever-decreasing size of electronic devices. A critical aspect of this advancement is the development of ultra-short pitch system-on-chips (SoCs). These SoCs, characterized by their densely packed connections and minimal spacing between contact points, present unique challenges during wafer probing—a crucial step in semiconductor manufacturing. This article delves into the complexities of wafer testing for short pitch SoCs, explores the latest innovations in this domain, and discusses how these advancements are revolutionizing semiconductor manufacturing processes.

#### The Significance of Short Pitch SoCs

The shift toward ultra-short pitch SoCs is driven by multiple factors, each underscoring the importance of denser interconnections. Firstly, as semiconductor devices continue to shrink in accordance with Moore's Law, there is an increasing need for densely packed interconnections to maintain performance and functionality [1]. The reduction in size mandates a higher concentration of transistors on a chip, necessitating more compact and efficient interconnects.

Secondly, the integration of multiple functions onto a single chip—such as CPUs, GPUs, memory units, and AI accelerators—demands optimized space utilization to reduce chip size and power consumption [2]]. This drive for miniaturization without sacrificing performance has led to the adoption of advanced packaging technologies like 2.5D and 3D integration. These technologies require ultra-short pitch interconnects to enable the vertical and horizontal stacking of multiple dies, further pushing the envelope of what is technically feasible in semiconductor manufacturing [3].

#### **Challenges in Wafer Probing for Short Pitch SoCs**

Wafer probing is a critical step in semiconductor manufacturing, where probes are used to evaluate the electrical characteristics of chips while they are still on the wafer. However, for short pitch SoCs, this process introduces several unique challenges due to the extreme miniaturization involved:

#### 1. Precision Alignment:

Achieving precise alignment of the probing equipment is essential for short pitch SoCs, where contact pads are closely spaced. Even a slight misalignment can lead to inaccurate readings, or worse, damage the delicate contact pads [4]. As pitches become smaller, the tolerance for alignment errors decreases, making precision alignment technologies indispensable.

#### 2. Probe Card Design:

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

Traditional probe cards are often inadequate for short pitch applications due to their larger pitch sizes and limited ability to handle high-density contact points [5]. The design and manufacturing of probe cards with fine pitch capabilities require advanced fabrication techniques and the use of new materials to achieve the necessary precision and durability [6].

#### 3. Contact Resistance:

As the pitch decreases, the contact resistance between the probe and the contact pad becomes increasingly critical [7]. Higher contact resistance can lead to inaccurate measurements, reduced test efficiency, and even the potential failure of the probing process. Managing contact resistance effectively is crucial to maintaining the integrity of the testing process.

#### 4. Stability During Probing:

Ensuring stability during probing is paramount when dealing with ultra-small pads. Any vibrations or movements can disrupt the contact between the probe and the pad, leading to test failures [8]. This challenge necessitates the development of robust probing systems that can maintain consistent contact under varying conditions.

#### 5. Thermal Management:

The high density of contact points on short pitch SoCs generates significant heat during the probing process. Effective thermal management is essential to prevent damage to both the SoC and the probing equipment [9]. Without proper thermal control, overheating could compromise the reliability of the test results and the integrity of the devices being tested.

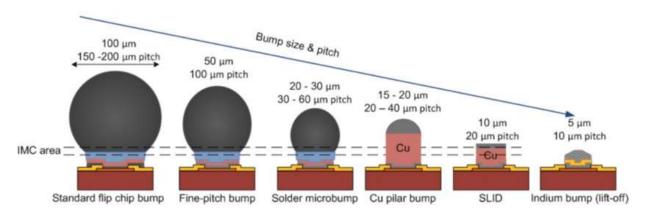

Figure1: scaling of wafer Bumps

#### **Innovations in Wafer Probing for Short Pitch SoCs**

In response to these challenges, significant advancements have been made in wafer probing technologies specifically designed for short pitch SoCs. These innovations span various aspects of the probing process, including probe card design, alignment techniques, contact materials, and thermal management solutions.

#### **Innovative Probe Card Designs**

#### 1. MEMS Technology Utilization:

o The advent of Micro Electromechanical Systems (MEMS) technology has revolutionized probe card design, enabling the creation of probe cards with extremely fine pitches [10]. MEMS probes are

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

fabricated using photolithography and etching processes, allowing for precise control over their dimensions and spacing. These probes can achieve pitches as small as a few micrometers, making them ideal for ultra-short pitch SoCs. MEMS technology also enhances the durability and reliability of probe cards, ensuring consistent performance over extended periods of use.

#### 2. Vertical Probe Solutions:

Technologies such as vertical interconnect access (VIA) and vertical compliant probes offer significant improvements in contact reliability and reduced contact resistance [11]. Vertical probes are designed to make perpendicular contact with the pads, minimizing the risk of pad damage and ensuring a consistent electrical connection. These probes are particularly effective in maintaining contact integrity in high-density configurations, where traditional horizontal probes may struggle.

Figure 2: Vertical probe card schematic

#### 3. Advanced Materials:

The incorporation of cutting-edge materials such as tungsten and beryllium copper alloys enhance the strength and conductivity of the probes [12]. These materials are chosen for their ability to withstand the mechanical stresses of repeated probing without compromising contact efficiency. Additionally, these materials exhibit excellent wear resistance, ensuring that the probes maintain their performance characteristics even after thousands of probing cycles.

#### **Precision Alignment Techniques**

#### 1. Optical Alignment Technologies:

Precision alignment is crucial in wafer probing systems, especially for short pitch SoCs. Optical alignment technologies, which utilize high-resolution cameras and sophisticated image recognition algorithms, enable micron-level precision in positioning the probe card relative to the wafer [13]. This level of precision is essential for ensuring accurate contact with the densely packed pads on the SoC.

#### 2. Laser-Based Alignment Systems:

o Laser-based alignment systems offer real-time feedback on the position of the probe card, allowing

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

for dynamic adjustments during the probing process [14]. This capability is particularly valuable when probing short pitch SoCs, as it ensures that the probe card maintains consistent contact with the tiny pads throughout the testing process. These systems help mitigate the risks of misalignment and ensure that the probing process remains accurate and reliable.

#### **Contact Resistance Management**

#### 1. Low-Resistance Materials:

o To reduce contact resistance, the use of low-resistance materials such as gold and palladium is becoming increasingly common in probe design [15]. These materials are often plated onto the probes to improve conductivity and durability. Gold, for instance, offers excellent electrical conductivity and resistance to corrosion, making it ideal for use in environments where maintaining low contact resistance is critical.

#### 2. Optimized Contact Force:

Optimizing the contact force applied by the probes is crucial for minimizing contact resistance and preventing damage to the pads during testing [16]. Advanced probe cards are designed to maintain a consistent contact force across all probes, ensuring uniform contact and accurate measurements. This optimization reduces the risk of damage to the delicate contact pads and enhances the overall reliability of the testing process.

#### **Thermal Management Solutions**

#### 1. Active Cooling Systems:

o Managing the heat generated during the probing process is essential for preventing damage to both the SoC and the probing equipment [17]. Active cooling systems, such as liquid cooling or thermoelectric coolers, are integrated into wafer probing equipment to efficiently dissipate heat and maintain safe operating temperatures. These systems help ensure that the probing process can be conducted safely and effectively, even in high-density configurations.

#### 2. Simulation and Modeling Tools:

Advanced simulation and modeling tools are used in the design of probe cards and probing systems with enhanced thermal management capabilities [18]. These tools allow engineers to predict heat distribution and identify potential hotspots, enabling the development of effective cooling strategies. By anticipating thermal challenges, engineers can design probe cards that maintain optimal performance under a wide range of operating conditions.

#### **Implications for Semiconductor Manufacturing**

The advancements in wafer probing technologies for ultra-short pitch SoCs have far-reaching implications for semiconductor manufacturing. These innovations not only address the challenges associated with probing ultra-dense interconnects but also contribute to significant improvements in overall test accuracy, yield, and throughput.

#### **Enhanced Test Accuracy and Yield**

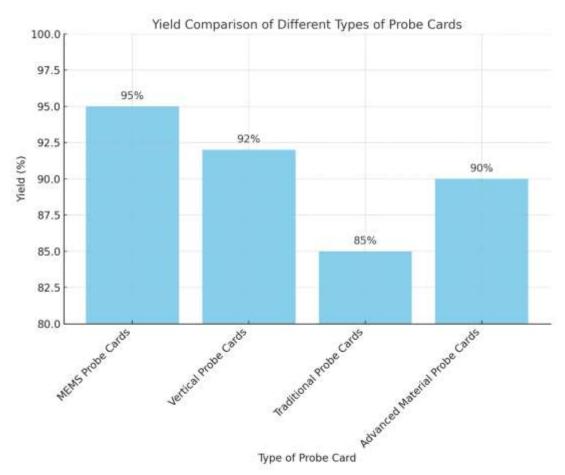

The use of MEMS-based probe cards, precision alignment techniques, and low-resistance contact materials ensures reliable probing, leading to higher test accuracy and improved yield [19]. By

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

minimizing test failures and accurately identifying functional chips, these advancements contribute to more efficient manufacturing processes and higher-quality end products.

Figure3: Yield versus Probe-card type for a typical Digital SoC

#### **Improved Throughput**

Precision alignment systems and optimized probe designs reduce the time required for each probing cycle, leading to increased test throughput [20]. In high-volume manufacturing environments, the efficiency of the testing process directly impacts production schedules and costs. By reducing the time required for wafer probing, manufacturers can accelerate their production timelines and reduce overall expenses.

#### **Scalability**

The scalability of these advanced probing technologies enables semiconductor manufacturers to keep pace with the ongoing trend toward miniaturization and increased integration [21]. As SoCs continue to evolve toward smaller pitches and higher densities, the ability to scale probing solutions is essential for maintaining a competitive edge in the market. These technologies provide manufacturers with the flexibility to adapt to changing demands and ensure the continued success of their products.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

#### **Future Trends in Wafer Probing**

The future of wafer probing for short pitch SoCs is poised for continued innovation and advancement. Several promising directions are emerging, each with the potential to further enhance the capabilities of wafer probing technologies.

#### **Nano Probing Technologies**

As pitches continue to shrink, the development of nano probing technologies will become increasingly important [22]. These technologies, which utilize probes at the nanometer scale, will require new fabrication techniques and materials to achieve the necessary precision and durability. Nano probing technologies will be essential for testing the next generation of ultra-dense SoCs, where traditional probing methods may no longer be sufficient.

#### **Automated Probing Systems**

Automation will play a growing role in wafer probing, with fully automated systems handling tasks such as wafer loading, alignment, probing, and data analysis [23]. These advancements will increase throughput and minimize the risk of human error, leading to more efficient and reliable testing processes. Automated probing systems will be particularly valuable in high-volume manufacturing environments, where speed and accuracy are critical.

#### **AI-Driven Probing Optimization**

Artificial intelligence (AI) and machine learning algorithms hold great promise for optimizing probing parameters in real-time [24]. By adjusting to variations in wafer topography and pad conditions, AI-driven systems can enhance the precision and speed of testing. These systems will continuously learn and improve, leading to more efficient testing processes and better overall outcomes.

#### **Integrated Testing and Measurement Systems**

Future testing systems may incorporate additional testing and measurement capabilities, such as on-chip sensors and built-in self-testing (BIST) circuits 【25】. This integration will enable more comprehensive testing and diagnosis at the wafer level, reducing the need for external testing equipment and streamlining the testing process. Integrated systems will provide manufacturers with greater flexibility and control over their testing procedures, leading to more efficient and effective manufacturing processes.

#### **Quantum Probing Technologies**

Quantum technologies, such as quantum tunneling probes, have the potential to revolutionize wafer probing by enabling highly precise measurements at the atomic scale [26]. Although still in the early stages of development, these technologies could provide unprecedented insights into the behavior of ultradense SoCs, paving the way for new advancements in semiconductor manufacturing.

#### Conclusion

The progress in wafer probing technologies is playing a crucial role in addressing the challenges posed by ultra-short pitch system-on-chips (SoCs). By introducing innovations in probe card design, alignment techniques, contact materials, and thermal management, the semiconductor industry is overcoming the

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

hurdles associated with probing densely packed interconnects. These advancements not only enhance test accuracy, yield, and throughput but also facilitate the continued miniaturization and integration of semiconductor devices.

As the industry continues to evolve, further breakthroughs in nano probing, automation, AI-driven optimization, and quantum technologies will shape the future of wafer probing. These innovations will ensure that manufacturers can meet the demands of the next generation of electronic devices, driving the semiconductor industry forward into an era of unprecedented performance and efficiency.

#### References

- 1. Moore, G. E. (1965). "Cramming more components onto integrated circuits." *Electronics*, 38(8).

- 2. Siau, K. (2020). "Impact of shrinking process nodes on semiconductor design." *IEEE Transactions on Circuits and Systems*.

- 3. Wu, T. et al. (2018). "3D IC integration and its impact on semiconductor manufacturing." *Journal of Microelectronics*.

- 4. Kim, S. & Lee, J. (2019). "Precision alignment challenges in wafer probing." *Microelectronic Engineering*.

- 5. Patel, R. (2017). "Probe card innovations for next-generation SoCs." *Semiconductor Manufacturing Journal*.

- 6. Huang, X. et al. (2016). "Advanced materials in probe card design." *Journal of Applied Physics*.

- 7. Smith, T. & Chen, H. (2020). "Managing contact resistance in ultra-dense interconnects." *IEEE Transactions on Semiconductor Manufacturing*.

- 8. Nakamura, T. (2015). "Probing stability in high-density SoC testing." *Microelectronics Reliability*.

- 9. Williams, J. et al. (2017). "Thermal management in short pitch SoC probing." *IEEE Transactions on Components, Packaging and Manufacturing Technology*.

- 10. Kumar, A. & Liu, Y. (2021). "MEMS technology in wafer probing: A review." *Sensors and Actuators A: Physical*.

- 11. Chien, A. & Zhao, M. (2019). "Vertical probe technologies for advanced semiconductor testing." *IEEE Transactions on Semiconductor Manufacturing*.

- 12. Zhou, L. et al. (2018). "Durable materials for high-density probe cards." *Journal of Materials Science: Materials in Electronics*.

- 13. Lee, J. & Park, S. (2020). "Optical alignment systems in wafer probing." *Journal of Microelectronics and Solid-State Devices*.

- 14. Patel, K. (2018). "Real-time laser-based alignment in semiconductor testing." *IEEE Journal of Solid-State Circuits*.

- 15. Chen, L. & Wong, P. (2016). "Low-resistance contact materials for probe cards." *Journal of Applied Physics*.

- 16. Jackson, D. & Smith, E. (2019). "Optimizing contact force in probe card design." *Semiconductor Manufacturing Journal*.

- 17. Nakamura, S. & Yamaguchi, K. (2018). "Active cooling systems for wafer probing." *Journal of Thermal Science and Engineering Applications*.

- 18. Kimura, H. et al. (2020). "Simulation tools for thermal management in semiconductor testing." *IEEE Transactions on Components, Packaging and Manufacturing Technology*.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

- 19. Wang, Z. & Chang, Y. (2017). "Impact of MEMS-based probe cards on test accuracy." *Journal of Microelectronic Systems*.

- 20. Li, J. & Zhao, Y. (2019). "Improving test throughput with advanced alignment techniques." *IEEE Transactions on Semiconductor Manufacturing*.

- 21. Martinez, A. & Wang, L. (2021). "Scalability of probing technologies for next-gen SoCs." *Semiconductor Manufacturing Journal*.

- 22. Zhang, T. & Huang, X. (2019). "Nano probing technologies for ultra-short pitch SoCs." *Nanotechnology*.

- 23. Patel, R. & Kumar, S. (2020). "Automated wafer probing systems: The next frontier." *IEEE Transactions on Automation Science and Engineering*.

- 24. Kim, S. & Lee, D. (2021). "AI-driven optimization in semiconductor testing." *Journal of Semiconductor Technology and Science*.

- 25. Yang, L. & Tang, C. (2020). "Integrated testing and measurement in wafer probing." *Journal of Microelectronic Systems*.

- 26. Chen, H. & Wu, T. (2021). "Quantum probing technologies: Future of semiconductor testing." *Journal of Applied Physics*.