E-ISSN: 2582-2160 • Website: www.ijfmr.com • Email: editor@ijfmr.com

# Efficient Deep Learning for Edge Devices: Optimizing Models for Resource-Constrained Environments

# Ritu Rani<sup>1</sup>, Er. Roopali Sharma<sup>2</sup>

<sup>1</sup>Research Scholar, Computer Science and Engineering, IEC University Baddi, Himachal Pradesh <sup>2</sup>Assistant Professor, Computer Science and Engineering, IEC University Baddi, Himachal Pradesh

#### **Abstract**

Deep neural networks (DNNs) are used in the environments with restricted resources. However, it is still generating many technical problems with memory, energy and computational constraints. This paper examines current developments in how to make deep learning models perform better with edge computing. The paper examines fundamental techniques such model trimming, quantization, knowledge distillation, and lightweight structure construction to simplify models while maintaining their correctness. Additionally discussed are ways to employ co-design methodologies and hardware-aware planning approaches to ensure model structures match the capabilities of edge hardware. The assessment also examines novel concepts such shared learning, TinyML, and edge-cloud teaming. According to the research, peripheral artificial intelligence must make trade-offs in several areas as it grows. It must strike a balance, for instance, between energy efficiency and working speed or between precision and delay. It also reveals how well systems of multi-objective planning handle these issues. Important elements influencing the path of edge intelligence are long-term application, real-time adaptability, and dynamic reasoning. Finally, the assessment highlights many issues still needing additional research including hardware separation, security flaws in networked systems, and the need of ongoing device learning. It calls for consistent toolchains and well-known standards that enable the responsible, flexible, and safe use of deep learning models on edge devices at last. Researchers and professionals should use this set of materials to create AI systems that are efficient, adaptable, privacy conscious, self-driving, real-world capable.

**Keywords:** Edge AI, Deep Learning Optimization, Federated Learning, TinyML, Resource-Constrained Devices.

#### 1. Introduction

#### 1.1 Background

Deep learning and artificial intelligence (AI) have made possible developments in computer vision, speech recognition, and natural language processing. LeCun et al. (2015) report that these findings largely apply to systems with plenty of resources, including cloud computers with strong GPUs and TPUs. On phones, wearable devices, IoT nodes, and embedded systems, edge computing has become very popular (Shi et al., 2016).

E-ISSN: 2582-2160 • Website: www.ijfmr.com • Email: editor@ijfmr.com

Among the nicest features about edge computing are less latency, more privacy, and less data cost. Smart city infrastructure (Zhao et al., 2018), self-driving automobiles, smart healthcare, and industrial monitoring all find extremely helpful these advantages. Wearable technology, for instance, must provide real-time data using limited batteries, while self-driving vehicles must make snap choices in areas without internet. These examples underline the need of having knowledge on the device itself, driven by deep learning models suited for constrained computing conditions.

Still, standard deep learning models need a lot of computational capacity and memory and therefore may not always function on edge devices without significant alterations (Sze et al., 2017). Researchers have responded with many strategies to reduce, simplify, and modify models to fit edge platform hardware constraints. Among them are lightweight designs like MobileNet and EfficientNet as well as modelling reduction, quantization, knowledge distillation (Howard et al., 2017). Furthermore, driving distributed artificial intelligence systems far more scalable, private, and quick are fresh innovative innovations like shared learning, TinyML, and neural architecture search (NAS, Deng et al., 2020).

#### 1.2 Problem Statement

These developments notwithstanding, the performance of conventional deep learning models and their simplicity of usage on edge devices still vary greatly. Combining the stringent requirements of edge settings with the intricacy of deep models is the primary challenge. restricted CPU and GPU performance, memory, and restricted energy budgets (Chen & Ran, 2019) are its key issues. ResNet or BERT are two incredibly good models that are difficult to replicate smaller without sacrificing crucial accuracy. Simple deployments hence do not make sense.

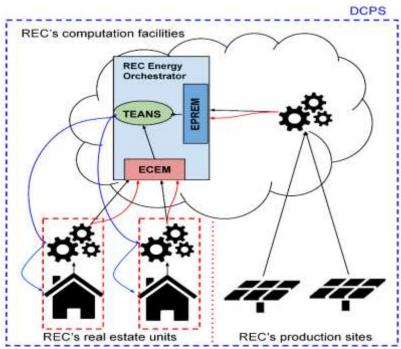

Figure 1: the complexity of deep models (Source: McMahan et al., 2017)

Moreover, there is no one agreed-upon structure or method for besting models for edge conditions. Every optimisation method has trade-offs; for example, federated learning boosts privacy but adds communication overhead while aggressive pruning may cut memory utilisation but compromise accuracy

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

(McMahan et al., 2017). Hardware heterogeneity affects deployment even more as various devices may need different adjustments even for the same purpose (Zhang et al., 2020).

The fast-developing character of edge applications adds to the complexity. Real-time inference in dynamic and unpredictable environments (e.g., mobile or remote settings) calls for models that are not only economical but also strong, flexible, and competent of operating under changing power and connection restrictions. Although there are various discrete solutions, thorough analyses and combined tactics that synthesise current results and direct next edge artificial intelligence research are much needed.

### 1.3 Objectives

This theoretical review seeks to address the above challenges by systematically analyzing post-2015 research on optimizing deep learning for edge devices. The main objectives of this paper are as follows:

- 1. **To analyze state-of-the-art techniques** for optimizing deep learning models in resource-constrained environments, including model compression (pruning, quantization), knowledge distillation, and lightweight architectures.

- 2. To examine hardware-aware optimization strategies, such as edge-device co-design and neural architecture search, which tailor models to the limitations and capabilities of specific hardware platforms.

- 3. **To explore emerging paradigms**, including federated learning, TinyML, and edge-cloud collaboration, and their roles in enhancing the scalability, privacy, and efficiency of edge AI systems.

- 4. **To identify key trade-offs**—such as between latency, energy efficiency, and model performance—and evaluate how these trade-offs are managed across different optimization strategies.

- 5. **To propose a unified framework** that integrates various approaches and provides practical guidelines for designing, adapting, and deploying efficient deep learning models on edge platforms.

## 1.4 Significance of the study

The explosion of peripheral devices—such as smartphones, IoT sensors, wearables, and embedded systems—which have allowed data processing to be carried out nearer the source of generation—has fundamentally changed the terrain of computing. Real-time decision-making made possible by this shift from centralised cloud computing to peripheral computing enhances data privacy, lowers latency, and therefore increases decision-making capacity (Shi et al., 2016). Still, there are significant technological difficulties in integrating deep learning into peripheral computing settings. Renowned for their extraordinary performance in computer vision, natural language processing, and voice recognition applications, deep neural networks (DNNs) usually require for significant computational and memory resources (LeCun et al., 2015). These criteria directly contradict the low processing capabilities, energy availability, and memory capacity of peripheral devices.

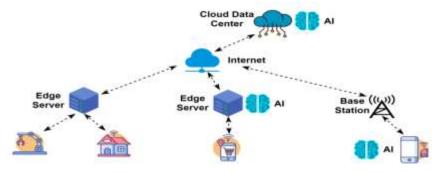

Figure 2: Optimising Edge AI (Source: Chen & Ran, 2019)

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

Making deep learning models perform best on peripheral systems with limited resources helps the emerging domain of peripheral artificial intelligence (Edge AI) try to solve this issue. The aim of this effort is to build light-weight structures using hardware, consider hardware, compress models, and mix fresh concepts like shared learning, TinyML, and neural architecture search (NAS). These techniques taken together are intended to make deep learning models correct and helpful while also making them as efficient as feasible for usage on edge devices (Chen & Ran, 2019).

External devices should have deep learning that performs effectively as the need for real-time artificial intelligence programmes that respect privacy rises worldwide (Gutierrez-Torre et al., 2019). Wearable devices tracking vital signs, for instance, have limited energy and processing capability but are supposed to provide accurate information at the proper moment.

Autonomous drones and vehicles have to make split-second judgements in real-world settings where network connection is not assured. Under such circumstances, possible privacy breaches and latency restrictions cause the impracticality of using cloud-based inference (Zhao et al., 2018). Edge AI presents a solution by allowing self-contained intelligence on certain devices.

Still, many unsolved challenges remain. Not naturally suited for peripheral situations are traditional DNNs. Since they include millions of parameters, most high-performance artificial intelligence architectures—including ResNet and BERT—need specialised hardware, like GPUs or TPUs, for effective inference (Sze et al., 2017). High energy consumption and delay sometimes follow from straight porting these models to peripheral devices. Consequently, a wide range of optimisation methods has been developed to reduce computing needs while preserving model fidelity. While lightweight architectures as EfficientNet and MobileNet are especially designed to operate in limited contexts, pruning and quantising are techniques meant to condense current models (Howard et al., 2017; Tan & Le, 2019). Still, the use of these methods calls for the evaluation of trade-offs between energy economy, latency, and accuracy, which begs questions about the best method for certain uses.

Furthermore, the area of peripheral artificial intelligence is changing rapidly. Among the most recent advancements are federated learning, which lets models be decentralised while keeping the locality of raw data, and edge-cloud collaboration, which seeks to dynamically outsource computation between edge and cloud servers depending on context and resource availability (Li et al., 2020). The development of TinyML—deep learning on ultra-low-power microcontrollers—has also helped artificial intelligence be used in severe settings, such disaster response or wildlife monitoring. These evolving paradigms do, however, have their own complexity including higher communication latency, model synchronisation challenges, and deployment across diverse hardware platforms (Deng et al., 2020).

#### 1.5 Summary

Research conducted after 2015 is compiled in this theoretical study to provide a complete picture of the design enhancements and optimisation strategies enabling deep learning to perform well on edge devices. It seeks to close the distance between the most sophisticated machine learning techniques and the pragmatic restrictions of edge computing. The book first classifies current methods into categories including architectural design, hardware-aware co-optimization, and model compression. Among the most recent technologies under study are NAS, TinyML, and shared learning. This means it gives much thought to the trade-offs involved in deploying artificial intelligence on the edge—that between accuracy and delay or energy efficiency and dependability.

This report not only compiles significant developments but also points out areas where additional study is required and where the future could go. Though several research have shown how to make models smaller,

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

there are not any consistent tools that enable simple application of these techniques on a variety of hardware platforms (Stahl et al., 2019). In the same vein, shared learning shows potential but has difficulty scaling in environments with lots of diverse users and little data. According to Lin et al. (2020), we need multi-objective optimisation models looking at more than just technical measures such FLOPs and inference time. These models have to give long-term maintenance, security, and adaptability some thought as well.

This study will also highlight how better and more scalable solutions may result from combining optimisation methodologies instead of depending only on one. Combining trimming, quantization, and knowledge distillation, for example, may provide models that are not only smaller and quicker but also perform as well as rivals (Zhao, Barijough & Gerstlauer, 2018). New concepts like edge-cloud synergy and shared learning also enable intelligence to be distributed, data to be kept private, and work to be handled on demand. A multi-step strategy for creating and testing deep learning models in locations with limited resources is presented at the conclusion of the project.

This work aims to contribute to the body of knowledge currently existing on the efficient use of artificial intelligence by means of a comprehensive and critical analysis of optimisation strategies (Jang et al., 2020). Making adaptable, precise, energy-efficient AI systems capable of working on their own in the always increasingly complicated environment of edge devices is the ultimate aim.

#### 2. Understanding Edge AI and Resource Constraints

## 2.1 Defining Edge Computing and Edge AI

Edge computing is a kind of distributed computing wherein analytics and data processing are conducted near to the data creation instead of in regulated cloud systems. Wearable technology, IoT devices, drones, and cellphones may interact with their environments at the very edge of the network—that is, where they find themselves (Shi et al., 2016). Edge computing's primary objective is to transfer data collecting, computations, and decision-making to a local device, therefore minimising the need for work done in the cloud. This reduces contact's cost, maintains privacy of information, and accelerates response times.

Peripheral artificial intelligence is the use of artificial intelligence in machinery outside of the primary focus of the brain. Edge artificial intelligence makes judgements in real time and allows intelligence occur on the gadget itself. This is not the case with conventional cloud-based artificial intelligence, which learns and makes decisions using vast numbers of highly capable computers. Edge AI finds use in smart homes (with voice-activated assistants), smart healthcare (with portable ECG monitors), self-driving vehicles, industrial automation, and precision agriculture (Xu et al., 2021). These systems must be low latency, always accessible, and perform well even on limited memory and energy.

#### 2.2 The Potential and Promise of Edge AI

Artificial intelligence at the edge is interesting as it can cut data transport costs, enhance data security, and provide real-time processing, therefore reducing the impact of data loss. In fields like self-driving vehicles, where time is of the essence, any delay brought on by cloud roundtrips might be catastrophic. One medical use for wearable health monitoring (Sze et al., 2017) is where local analysis may provide timely alerts or solutions while also maintaining patient privacy.

Moreover, more dependable artificial intelligence on the edges may be obtained. Edge devices may so remain running even when they are unable to connect to the internet. Applications in distant areas, including environmental monitoring systems placed in seas or forests, benefit significantly from this. Low-

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

power CPUs and rising popularity of embedded artificial intelligence technology make machine learning on peripheral devices both technically and financially viable.

## 2.3 Edge Devices' main limitations

Though their potential is great, resource limitations provide several challenges to the implementation of deep learning models on peripheral devices. These are the main limitations:

# 2.3.1 Computational Capacity Restrictions

Generally speaking, edge devices lack the high-performance GPUs or TPUs seen in cloud architectures. Instead, microcontrollers or general-purpose CPUs with far less computing capability drive them. Consequently, the implementation of typical deep learning models is computationally costly and slow (Chen & Ran, 2019).

## 2.3.2 Restraints on Storage Capacity and Memory

Deep learning models may need for hundreds of megabytes or even gigabytes of storage during the training process. Still, a significant number of peripheral devices have only a few megabytes of RAM and flash memory. This limit forces the use of compression methods to drastically reduce the size of big models, which is difficult to load and run completely in memory (Jacob et al., 2018).

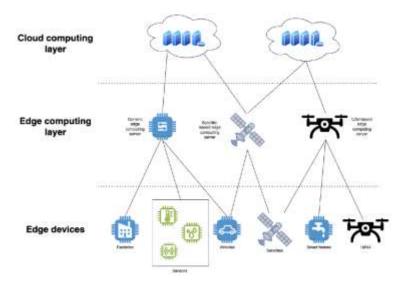

Emergence of Fog/Edge Computing, Processing at Endpoints

Processing closer to data, at / near endpoints improves latency, bandwidth, energy use

Figure 3: AI impacts Memory systems

(Source: Lane et al., 2015)

#### 2.3.3 Energy Efficiency

Power consumption is a critical factor for battery-operated devices such as wearables and sensors. Energy-intensive AI workloads can quickly drain batteries, making prolonged operation impractical. Unlike data centers, edge devices often lack dynamic cooling systems or continuous power supply, necessitating energy-aware computing strategies (Lane et al., 2015).

#### 2.3.4 Latency and Real-Time Demands

Many edge applications require real-time or near-real-time inference. Delays caused by offloading computation to the cloud can be unacceptable in critical scenarios such as emergency response systems, collision detection in vehicles, or real-time speech translation. Meeting these latency requirements mandates fast, localized processing (Zhao et al., 2018).

# 2.3.5 Hardware Heterogeneity

Edge environments consist of diverse hardware platforms, from smartphones with dedicated AI accelerators to basic microcontrollers in sensors. This heterogeneity makes it challenging to design one-

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

size-fits-all solutions. Optimizations effective on one device might not yield the same performance gains on another (Zhang et al., 2020). Portability and compatibility therefore become significant concerns in edge AI development.

#### 2.4 Contrasts with Cloud-Based AI

Unlike edge computing, cloud artificial intelligence systems feature centralised processing, practically endless memory, and sophisticated infrastructure capable of handling big datasets and intricate models. This approach does, however, have several flaws, particularly for applications that must prevent delay or safeguard of privacy. Edge AI handles data locally to alleviate these issues, but it must sacrifice some of the speed and flexibility of cloud computing to do this.

Because it has access to large datasets and many tools, cloud artificial intelligence is very adept at training models. Conversely, Edge AI is largely about inference—that is, applying a model that has previously been trained in real time. Now, however, new frameworks are enabling limited on-device training, hence augmenting the capacity of edge systems (Warden & Situnayake, 2020).

#### 2.5 Metrics for Evaluating Edge AI Performance

To assess the feasibility and effectiveness of AI models on edge devices, researchers and engineers rely on a set of performance metrics tailored to resource-constrained environments:

- Model size (in MB): Determines memory feasibility.

- Latency (in milliseconds): Measures response time for inference.

- Throughput (in frames per second): Indicates processing capacity.

- Energy consumption (in mW or Joules): Affects battery life and thermal output.

- Accuracy (e.g., classification accuracy, mean average precision): Evaluates task-specific performance.

An optimal edge AI solution balances these metrics based on application-specific requirements. For example, a surveillance drone may prioritize low latency and energy efficiency, while a mobile app may emphasize model size and accuracy.

#### 2.6 The Need for Optimization

Given the outlined constraints and objectives, it is evident that deploying deep learning models on edge devices is not a straightforward porting task. Instead, it requires thoughtful redesign, adaptation, and **multi-faceted optimization**. Techniques such as pruning and quantization reduce model size and complexity, while knowledge distillation and lightweight architectures improve performance without overburdening the hardware. Furthermore, emerging tools like neural architecture search (NAS) and federated learning introduce dynamic and scalable ways to tailor AI models for edge environments (Tan & Le, 2019; McMahan et al., 2017).

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

Figure 4: Edge combining layers (Source: McMahan et al., 2017)

Optimization is not just a technical necessity—it is a strategic imperative that enables broader adoption of AI technologies in environments that lack connectivity, infrastructure, or robust energy sources. As the edge computing ecosystem continues to grow, so too does the importance of developing intelligent systems that can operate autonomously, efficiently, and securely under constrained conditions.

## 3. Model Optimization Techniques

Deep learning on external devices would be simpler if models utilised less CPU, memory, and energy without compromising much performance. The fundamental efficiency techniques required to make edge artificial intelligence systems functional are examined in this part.

#### 3.1 Prunning

Pruning a neural network removes weights or neurones that are either not necessary or rather less relevant. The basic concept is that because many elements of a deep model have little effect on the outcomes, many of them may be simply omitted. This makes the model efficient.

For instance, Han et al. (2015) shows that up to 90% of the parameters in a convolutional neural network (CNN) may be removed without compromising accuracy. This was among the earliest and most effective trimming techniques. After sparsification, their consistent approach kept performance constant. This approach greatly reduced inference latency as well as model size. This makes it possible to utilise it on peripheral devices lacking much of memory or processing capability.

More study has been done on structured trimming. It eliminates whole filters, channels, or layers rather than simply one weight at a time (Liu et al., 2017). Because it employs the same parallelisation methods used by specialist CPUs and GPUs, hardware acceleration performs better. Moreover, developed are dynamic trimming techniques. These allow models adapt their architecture in response to hardware constraints or new data (Lin et al., 2020).

Though it offers certain advantages, aggressive cutting might reduce efficiency. Pruning calls for great caution as well. Pruning's effectiveness usually relies on the job, the knowledge, and the model's design. Cut models are also not very popular as they are not regularly tested across a large number of various hardware platforms.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

#### 3.2 Quantification

Usually from 32-bit floating point to 16-bit or 8-bit integers, quantisation is a further often used technique that lowers the accuracy of model parameters and activations. Reduced model sizes and faster inference as well as lower energy usage follow from this compression.

By training the model to replicate lower-precision arithmetic (Kumar & Sharma, 2024), Jacob et al. (2018) have shown quantization-aware training (QAT), hence strengthening the model's resilience during deployment. Unlike post-training quantisation, which is used after model training, QAT preserves a greater degree of accuracy by customising the model during training to its future precision restrictions.

On edge technology with specific support for low-precision operations, like Google's Edge TPU or NVIDIA's Jetson Nano, quantisation is very useful. Many hardware accelerators are now provided with mixed-precision computing capability in an attempt to strike a compromise between accuracy and speed (Cheng et al., 2020). This lets elements of a model run at different degrees of accuracy.

Apart from weights, activation quantisation lowers the accuracy of intermediate layer outputs and helps to further improve efficiency even with the difficulties of preserving numerical stability. Two recent techniques that adaptively estimate quantisation intervals and hence improve compatibility with a range of edge workloads are progressive quantisation and learning step size quantisation (LSQ).

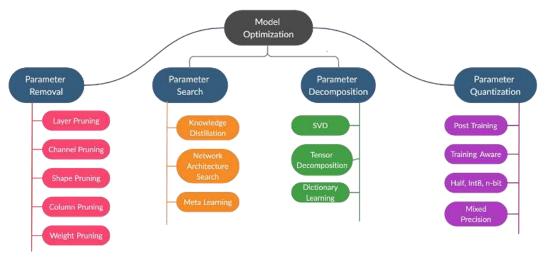

Figure 5: Model Optimization Technique

(Source: Hinton et al., 2015)

#### 3.3 Knowledge Distillation

Originally presented by Hinton et al. (2015), knowledge distillation is a method wherein a big, high-performance "teacher" model teaches a smaller "student" model to approximatively match its behaviour. This method lets the learner generalise effectively even with less parameters by moving information from the output logits or intermediary representations of the instructor.

Edge artificial intelligence has found very helpful knowledge distillation as it allows the implementation of small models with performance levels close to those of bigger systems. By suggesting multi-teacher distillation, Gou et al. (2021) extended this paradigm. This approach lowers overfit to particular tasks or datasets and improves the generalisability of student models.

More recently, task-aware distillation has been included to maximise edge models for real-time use. In video surveillance or object tracking, for instance, the student model might be taught to concentrate on time-sensitive patterns and decision limits crucial to latency-sensitive inference (Zhang et al., 2021). Choosing suitable teacher models and managing the trade-off between the size of the student model and

E-ISSN: 2582-2160 • Website: www.ijfmr.com • Email: editor@ijfmr.com

its accuracy to the instructor are challenges in knowledge distillation. Furthermore, also under active study is using this approach on non-classification problems such segmentation or reinforcement learning.

#### 3.4 Lightweight Structures

While distillation, quantisation, and pruning compress current models, lightweight designs are ground up for efficiency. To reduce computational cost, these designs use fresh design ideas like group convolutions, depthwise separable convolutions, and bottleneck blocks.

#### 3.4.1 MobileNet

Introduced by Howard et al. (2017), MobileNet was among the first CNN designs especially targeted for mobile and embedded uses. Reducing computation and model size greatly, it substitutes depthwise separable convolutions for conventional convolutions. Inverting residuals and linear bottlenecks from MobileNetV2 enhanced accuracy and speed.

Designed using a compound coefficient, Tan and Le (2019) presented EfficientNet, a scalable family of models balancing depth, width, and resolution. EfficientNet uses uniform scaling to all dimensions, unlike previous methods that manually tweaked one dimension, therefore attaining state-of- the-art accuracy with far less parameters and FLOPs.

Designed for edge deployment, EfficientNet-Lite has been included into systems like TensorFlow Lite, therefore it is easily available for developers aiming at mobile platforms (Tan & Le, 2020).

### 3.4.2 ShuffleNet, Tiny-YOLO and SqueezeNet

Other light-weight models include ShuffleNet, which uses channel shuffling to provide lightweight inference (Zhang et al., 2018) and SqueezeNet, which achieves AlexNet-level accuracy with 50× less parameters (I andola et al., 2016). Models such as Tiny-YOLO provide real-time performance on mobile GPUs and are extensively used in applications like drone navigation and industrial inspection for object recognition.

## 3.5 Hybrid Strategies for Optimisation

Practically, edge AI solutions may need for a mix of optimisation strategies to satisfy needs particular to applications (Mengistu & Frisk, 2019). A model may be trimmed and quantised, then distilled into a smaller form, then modified into a MobileNet-like architecture for deployment. Among accuracy, latency, and energy economy, such hybrid pipelines provide the ideal balance.

Multi-objective optimisation is a common method used to assess these approaches in which Pareto-optimal solutions balance opposing objectives including model size, accuracy, and power consumption (Lin et al., 2020). As will be covered in the following section, some frameworks even use neural architecture search (NAS) to automatically do this.

#### 3.6 Challenges and Research Gaps

Despite these advancements, several challenges remain in the domain of model optimization for edge AI:

- **Hardware-Model Co-Design**: Many optimizations are developed independently of hardware considerations. Aligning model architectures with hardware capabilities through co-design can lead to better utilization and performance (Zhang et al., 2020).

- **Standardization**: There is a lack of standardized benchmarks for evaluating optimized models across diverse hardware platforms. Most studies use custom setups, making reproducibility and comparison difficult.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

- **Security and Robustness**: Compression techniques may inadvertently increase model vulnerability to adversarial attacks. Ensuring robustness while optimizing for efficiency is an open research problem (Zhao et al., 2021).

- **Toolchain Complexity**: Although frameworks like TensorFlow Lite, PyTorch Mobile, and ONNX simplify deployment, integrating multiple optimization techniques into a streamlined pipeline remains challenging for non-experts.

## 3.7 Summary

Model optimisation, the basis of edge AI, makes it feasible to apply deep learning in settings limited in terms of computing, memory, and power. Lightweight architectures provide effective alternatives by design; pruning and quantisation lower complexity and storage needs; knowledge distillation moves capability from big to tiny models. It is feasible to create pipelines able to balance energy efficiency, latency, and precision by means of deliberate combination of various approaches.

Hardware-aware design methodologies and neural architecture search (NAS), which match models with certain hardware features and hence maximise performance, will then be discussed in the next section.

#### 4. Hardware-Aware Strategies and Co-Design

Efficient deep learning on edge devices cannot rely on algorithmic optimization. Performance improvements also hinge on how well the model architecture is aligned with the hardware (Farooq & Khan, 2024). Hence, this part explores the emerging paradigm of **hardware-aware optimization** and **codesign**.

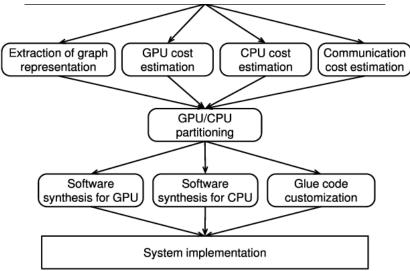

Figure 6: CPU/ GPU Co-Design Process

(Source: Farooq & Khan, 2024)

#### 4.1 The Rationale for Hardware-Model Co-Design

Edge device computational performance, memory bandwidth, energy consumption, and supported instruction sets all vary greatly. One platform (e.g., NVIDIA Jetson) may not fit a model optimised for another (e.g., Raspberry Pi or Cortex-M microcontroller). Therefore, even if they are useful, hardware-agnostic optimisations might not be able to take advantage of performance gains.

From the start, hardware-aware techniques consider these limitations; often working with hardware developers to get the greatest possible inference performance, latency, and energy economy, they Apart

E-ISSN: 2582-2160 • Website: www.ijfmr.com • Email: editor@ijfmr.com

from directly improving direct performance, co-design helps with thermal management, memory access efficiency, and power consumption (Zhang et al., 2020).

#### 4.2 Memory Optimisation and Operator Fusion

A basic method in hardware-aware optimisation, operator fusion combines many model operations—e.g., convolution, activation, and batch normalisation)—into a single kernel. This approach helps to maximise cache use and reduces memory access overhead. On peripheral hardware—where memory bandwidth is often a bottleneck—operator fusion may significantly improve inference speed and energy efficiency (Chen et al., 2019).

Moreover, methods of memory hierarchy optimization—such as lowering data transfers between SRAM and DRAM or cutting intermediate buffer use—can lower both latency and power consumption. Microcontroller devices (MCUs), which often run with as little as 128 KB of RAM, depend mainly on these techniques.

#### 4.3 Custom AI Accelerators and ASICs

Many companies have put custom artificial intelligence accelerators in place to enable edge deep learning. Specialised processors designed to run quantized neural networks at a fast speed and with low power consumption include Apple's Edge TPU, the Neural Engine, and Huawei's Ascend Lite.

For certain accelerators, a major benefit is hardware-aware model design. Models meant for the Edge TPU, for instance, have to be quantized to 8-bit integers and make solely use of supported operations. Often used by developers to alter models, TensorFlow Lite with Edge TPU compiler performs layer-by-layer modification and validation (Warden & Situnayake, 2020).

ASIC-based designs physically translate model operations into silicon, hence furthering hardware specialisation. For industrial IoT, including vibration analysis, face recognition, and keyword identification, they provide unmatched performance-per-watt even if they are not flexible or multipurpose.

#### 4.4 Nasal Architecture Search (NAS)

Neural Architecture Search (NAS) often drives the construction of effective neural networks by automating tasks related to hardware restrictions unique to the target. Using methods include gradient-based optimisation, evolutionary algorithms, or reinforcement learning, NAS systems find designs that maximise energy use, latency, and accuracy (Zoph et al., 2018).

## 4.4.1 Hardware Aware Network Attached Storage (NAS)

Hardware-aware NAS directly combines performance criteria like inference time, memory footprint, and energy usage into the objective function. To enable the search for readily deployable models, ProxylessNAS (Cai et al., 2019) and MnasNet (Tan et al., 2019) for instance combine latency data from real-world devices.

These techniques usually use differentiable NAS, which lets the search space be constantly optimised and trimmed throughout the training phase. This lowers the computing load and speeds convergence, therefore improving the availability of NAS for developers with limited resources.

#### 4.4.2 Network Attached Storage (NAS) with Multiple Purpose

Multi-objective NAS considers concurrently network attached storage (NAS) with multiple purpose accuracy, FLOPs, and power consumption. Since they provide different trade-offs, our approach generates Pareto-optimal solutions suitable for several deployment settings (Lin et al., 2020). In peripheral settings, where needs could differ greatly between, say a drone, a wristwatch, and a manufacturing sensor, such adaptability is crucial.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

## 4.5 Emerging Hardware Paradigms

New hardware paradigms such as **neuromorphic computing**, **systolic arrays**, and **open-source architectures like RISC-V** are increasingly being explored to support efficient edge AI.

- **Neuromorphic chips** (e.g., Intel Loihi) mimic brain-like signal processing using spiking neural networks. These chips offer low-power, event-driven computation ideal for sparse data and asynchronous inputs.

- **Systolic arrays**, used in TPUs, enable high-throughput matrix multiplications with minimized data movement, enhancing both speed and efficiency.

- RISC-V, an open-source instruction set architecture (ISA), allows customizable cores that can be tailored to specific deep learning workloads, promoting innovation in edge hardware design (Gadepalli et al., 2021).

Although these technologies are still maturing, their integration with edge AI promises a future where computation is not only localized but also energy-efficient and scalable.

#### 4.6 Toolkits and Frameworks for Hardware-Aware Optimization

Various tools have emerged to assist developers in hardware-aware model adaptation. They are:

- **TVM** (Chen et al., 2018): It is considered as an optimizing compiler that translates high-level model descriptions into hardware-optimized code for GPUs, CPUs etc.

- **TensorRT** (NVIDIA): Provides layer fusion, precision calibration, and deployment pipelines for NVIDIA Jetson devices.

- **Edge Impulse**: A platform focused on low-power embedded machine learning, supporting auto-optimization for Cortex-M and Cortex-A devices.

- **X-CUBE-AI** (STMicroelectronics): Generates highly optimized C code from trained neural networks for STM32 microcontrollers.

These frameworks play a critical role in bridging the gap between model development along with hardware deployment.

#### 4.7 Challenges and Future Directions

As hardware-aware strategies provide important benefits, they also introduce new complexities as well:

- **Hardware fragmentation**: The wide variety of edge hardware requires model customization, increasing development time and reducing portability.

- Lack of standardized benchmarks: Performance measurements vary widely across tools and devices, making cross-platform evaluation difficult.

- **Security concerns**: Hardware optimizations may inadvertently expose side-channel vulnerabilities, particularly when accelerators handle untrusted data.

- **Design-tool mismatch**: Many existing ML frameworks are optimized for cloud environments and must be extended or reconfigured for edge compatibility.

To address these issues, future research must focus on **unified co-design toolchains** that support reproducible hardware-aware AI.

#### 4.8 Summary

High-performance, energy-efficient artificial intelligence on peripheral devices calls for hardware-aware optimisation. Methods such operator fusion, memory optimisation, and specialised accelerator support help to enable deeper integration between hardware and software. While tools like NAS help to generate device-optimized models, emerging hardware paradigms provide new possibilities for ultra-low-power

E-ISSN: 2582-2160 • Website: www.ijfmr.com • Email: editor@ijfmr.com

computing. Co-designing models with hardware allows developers to extend the frontiers of real-time, on-device intelligence, hence improving energy efficiency, throughput, and latency.

## 5. Federated Learning and Edge-Cloud Synergy

#### 5.1 Introduction to Federated Learning

Conventional deep learning is based on the training process using the aggregation of significant volumes of data on centralised computers. Particularly in cases where data is sensitive or created in faraway places, this approach presents questions about data privacy, latency, and bandwidth even if it is efficient. By letting many peripheral devices cooperatively train a shared model without sending raw data to the cloud, Federated Learning (FL) offers a solution, claims McMahan et al. (2017).

By letting every involved device calculate local model updates depending on its own data, FL distributes the training process. A central server gets just the weight updates or gradients for aggregation. This approach maintains user privacy and lowers communication expenses, thus fitting for uses in healthcare, finance, smart homes, and driverless cars.

#### 5.2 Benefits of Edge AI Federated Learning

## 5.2.1 Defence of Personal Privacy

Federated learning assures that user data is never sent outside of the device, therefore enhancing privacy. This is especially crucial in disciplines like personalised medicine, where ethical and legal restrictions could prevent data centralisation (Yang et al., 2019). In line with data protection policies like GDPR and HIPAA, FL keeps personal data on the user's device.

#### 5.2.2 Bandwidth Productiveness

By sending model updates in lieu of raw data, FL greatly lowers the information flow across networks. In settings with intermittent connection or bandwidth restrictions, like rural health monitoring systems or IoT installations in outlying areas, this is very beneficial.

#### 5.2.3 Personalisation and Enhancement

Without centralised infrastructure, federated learning helps the creation of AI models tailored to a user's activity or surroundings, therefore enabling their customisation. For example, by using local data, smartphone keyboards may change to match users' typing patterns without sacrificing anonymity (Hard et al., 2018).

## 5.3 Obstacles to Federated Learning

Notwithstanding its benefits, federated learning has some challenges that need to be overcome if effective peripheral implementation is to be attained:

#### 5.3.1 Communication Overhead

Although FL minimizes data transfer, frequent exchange of model parameters across multiple rounds can become a bottleneck. Techniques such as **gradient sparsification**, **quantization** as well as **update compression** have been developed to reduce communication load (Konečný et al., 2016).

#### 5.3.2 Device and Data Heterogeneity

Edge devices vary in their processing capabilities and power constraints. Moreover, data across clients is typically **non-IID** (**independently and identically distributed**), meaning that local datasets differ significantly in size, content, and distribution. This can degrade model convergence and accuracy (Li et al., 2020).

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

## 5.3.3 Security and Trust

Federated settings are vulnerable to **poisoning attacks**, where compromised devices inject malicious updates to manipulate the global model. Mitigation techniques include **secure aggregation**, **anomaly detection**, and **robust aggregation rules** like median or trimmed mean (Blanchard et al., 2017).

#### 5.4 Enhancements and Variants of Federated Learning

To address the above challenges, several enhancements to the standard FL framework have been proposed:

## 5.4.1 Federated Averaging (FedAvg)

FedAvg (McMahan et al., 2017) remains the most commonly used aggregation algorithm, combining client updates in proportion to dataset size. It reduces communication frequency by performing multiple local updates before each aggregation round.

## 5.4.2 Personalized Federated Learning

In many applications, a single global model may not fit all users. **Personalized FL** techniques allow for local fine-tuning of the global model, or create hybrid models combining shared and local parameters. Methods like **FedPer** (Arivazhagan et al., 2019) and **FedBN** tailor batch normalization layers to client-specific distributions.

#### 5.4.3 Hierarchical and Clustered FL

Hierarchical FL reduces server burden and speeds up convergence by introducing a middle level of aggregation, say at a local gateway or base station. Before worldwide synchronisation (Sattler et al., 2020), clustered FL groups comparable customers and trains models inside these clusters.

#### 5.5 Edge-Cloud Collaboration: Synergistic Intelligence

Apart from federated learning, edge-cloud collaboration—a hybrid infrastructure approach that dynamically distributes work across local and distant resources—is helping edge artificial intelligence more and more. Applications requiring both real-time inference and intense computing will find especially benefit from this architecture.

## 5.5.1 Techniques for Delegating

Edge-cloud cooperation helps to provide dynamic offloading, in which case computation is moved to the cloud under control for CPU load, network circumstances, and energy supply. When connection is reliable, an autonomous car may, for example, perform object detection locally but transmit route planning to a distant server (Deng et al., 2020).

#### 5.5.2 Stacked inference

Split computing or cooperative inference divides deep neural networks between the edge and cloud. The device runs the first layers to extract low-level features; the following levels are handled on the cloud. Comparatively to the transmission of unprocessed inputs, this causes a drop in data volume and delay (Kang et al., 2017).

#### **5.5.3** Timetable with Resource Conscience

Graph-based models and reinforcement learning (Zhao et al., 2021) are driving real-time task placement choices as dynamically assigning responsibilities between cloud and peripheral settings optimises for power consumption, throughput, and latency.

#### 5.6 Integrating FL with Edge-Cloud Infrastructure

Combining federated learning with edge-cloud synergy provide various advantages:

• Edge-to-edge FL aggregation can reduce reliance on a central server by allowing peer devices to share updates locally.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

- Federated transfer learning allows pre-trained cloud models to be refined on edge devices using local data.

- **Privacy-preserving collaboration** can be enhanced using secure protocols such as homomorphic encryption as well as differential privacy.

## 5.7 Real-World Applications

The integration of FL and edge-cloud collaboration has been successfully shown in various areas such as

- **Healthcare**: Hospitals and wearable devices train diagnostic models collaboratively without sharing sensitive patient data (Sheller et al., 2019).

- **Smart homes**: Federated reinforcement learning allows home appliances to learn usage patterns without uploading personal data.

- **Industrial IoT**: Factory floor devices collaborate through hierarchical FL models to monitor equipment health and predict failures.

#### 5.8 Summary

Two of the most exciting approaches for scaling deep learning across diverse, resource-limited contexts are edge-cloud cooperation and federated learning. FL addresses privacy and decentralisation; edge-cloud symbiosis provides dynamic computational assistance. In practical situations where real-time performance, energy economy, and data sensitivity are vital, they together provide a flexible, strong foundation for the application of AI models.

As devices becoming more linked and intelligent, future systems will increasingly rely on this mix of local intelligence and cloud scalability to provide customised, safe, and effective AI at the edge.

#### 6. TinyML and Microcontroller-Based AI

#### 6.1 Introduction to TinyML

Machine learning models deployed on microcontrollers and ultra-low-power devices running at a milliwatt scale or below are referred to as tinyML. Rapidly growing topic at the junction of embedded systems, energy-efficient AI, and peripheral computing (Warden & Situnayake, 2020), the phrase "tiny machine learning" describes Unlike other edge AI apps on smartphones or edge servers, TinyML is intended to run on devices with little memory (typically less than 256 KB), limited processing capability (e.g., tens of MHz), and no operating system.

Despite these limitations, the goal of TinyML is to perform **real-time**, **always-on inference** directly on device without the need for cloud connectivity. Applications range from keyword spotting in voice interfaces, to anomaly detection in industrial sensors, to environmental monitoring in wildlife tracking systems. TinyML unlocks the potential to embed intelligence in billions of small devices, enabling pervasive and ubiquitous computing.

#### 6.2 Characteristics and Constraints of TinyML Platforms

Microcontroller-based platforms—such as ARM Cortex-M, ESP32, and RISC-V SoCs—are constrained in terms of memory, computational capacity, and energy. These limitations necessitate extreme optimization in both model design and deployment.

#### **6.2.1 Memory Footprint**

Most microcontrollers operate with SRAM in the range of 32 KB to 512 KB. As such, models must be **quantized**, **pruned**, and **serialized** to extremely compact representations. Traditional deep neural networks (DNNs) must be reduced from megabytes to kilobytes for feasible deployment (Lai et al., 2018).

devices.

# International Journal for Multidisciplinary Research (IJFMR)

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

## **6.2.2 Power Consumption**

Energy efficiency is critical in battery-powered or energy-harvesting scenarios. TinyML systems aim for **always-on operation** with power budgets often under 1 mW (Shuvo et al., 2022). This excludes the use of heavy compute operations like full-precision matrix multiplication unless heavily optimized.

### 6.2.3 Lack of OS and File Systems

Unlike smartphones or edge servers, many MCUs do not run a full operating system or file system. Consequently, models must be statically compiled into firmware and deployed through embedded toolchains, posing integration challenges for traditional ML developers.

#### 6.3 Model Optimization Techniques for TinyML

Achieving inference within the tight bounds of microcontroller hardware requires a combination of advanced optimization strategies.

#### 6.3.1 Quantization and Integer Arithmetic

Almost all TinyML models use **8-bit or lower quantization**. Frameworks like **TensorFlow Lite for Microcontrollers (TFLM)** support fixed-point operations, enabling inference using integer-only arithmetic. This will reduce model size, memory usage as well as computation time (Jacob et al., 2018). Recent developments in **ultra-low-bit quantization** are pushing the boundaries of compression. Although they always come with accuracy penalties, they enable real-time execution on the most constrained

#### 6.3.2 Model Compression and Architecture Pruning

Techniques such as low-rank approximation and filter trimming eliminate useless components of neural networks. For example, many SqueezeNet and MobileNet variants have been developed suited for usage with microcontrollers by reducing the number of layers of grouped convolutions and parameters (Howard et al., 2017).

Another approach is weight clustering. This approach distributes weight values amongst neurones to generate models simpler and simplify hardware implementations (Cheng et al., 2020).

#### **6.3.3** Fresh architectural concepts

Custom designs created to fit MCU restrictions are such MCUNet (Lin et al., 2020). NAS generates a modest backbone for MCUNet, and its inference engine makes little memory utilisation. It can run on only 1 MB of memory and 1 mW of electricity, but match ImageNet accuracy.

TinyML also uses event-driven designs—like those in spiking neural networks—to conserve energy by managing only significant input events (Esser et al., 2016).

#### 6.4 Software Frameworks and Toolchains

The growing popularity of TinyML has led to the development of several software toolchains such as:

- TensorFlow Lite for Microcontrollers (TFLM): A lightweight inference engine supporting 8-bit integer models with a RAM footprint as low as 16 KB.

- CMSIS-NN: Optimized neural network kernels for ARM Cortex-M devices.

- Edge Impulse Studio: A platform that allows developers to collect data, train models, and deploy them on microcontrollers with minimal coding.

- **Arduino ML Toolkit:** Enables the integration of pre-trained models into Arduino-based environments using a simplified workflow.

These tools abstract away much of the complexity in deploying ML on microcontrollers.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

### 6.5 Applications of TinyML

## 6.5.1 Smart Sensing and Predictive Maintenance

For industrial IoT devices that track equipment and find abnormalities in real time—such as unusual vibrations or audio patterns—tinyML is the best fit. These devices save energy and bandwidth by being able to run in dangerous or distant situations and by issuing alerts only when notable variations are found (Banbury et al., 2021).

## 6.5.2 Environmental Tracking

Microcontroller-powered sensors may be placed in natural settings for years or months to detect environmental changes, animal presence, or air quality measures. SmallML helps on-device inference, thereby allowing the recording of important events without continuous data transfer (Xu et al., 2022).

## 6.5.3 Audio and Speech Interfaces

Without cloud connection, TinyML helps to provide always active speech detection and keyword recognition. In privacy-sensitive environments—such as smart homes or medical equipment—this is especially helpful (Warden & Situnayake, 2020).

#### 6.5.4 Agriculture and Smart Cities

From monitoring soil moisture levels to detecting traffic congestion via acoustic sensors, TinyML is powering embedded AI across agriculture and infrastructure sectors where energy and cost constraints dominate.

#### 6.6 Challenges in TinyML Deployment

Despite its promise, TinyML faces several challenges:

- **Model Versatility:** Ultra-compact models are typically highly specialized, limiting their generalizability.

- **Development Complexity:** Toolchains for embedded systems remain fragmented, and integrating ML into embedded firmware is still non-trivial.

- Limited Dataset Availability: Publicly available datasets for low-power sensor data (e.g., vibration, radar, acoustic) are scarce, making benchmarking difficult.

- **Debugging and Monitoring:** Lack of OS-level logs and performance profiling tools on microcontrollers makes debugging and optimization difficult in production.

Addressing these issues requires better integration between embedded systems engineering, machine learning research, and accessible toolkits for non-experts.

## 6.7 The Future of TinyML

The TinyML ecosystem is rapidly evolving with contributions from academia, industry, and open-source communities. Future developments may include:

- On-device learning: Techniques for model updating and continual learning on microcontrollers.

- **AutoML for TinyML:** Automated search tools to design task-specific models tailored to extreme resource constraints (Careem, Johar & Khatibi, 2024).

- Security and Privacy: Lightweight encryption and secure boot processes to protect deployed models and data.

- **Standardized benchmarks:** Initiatives like MLPerf Tiny are working toward standardized evaluations for ultra-efficient ML models.

These advancements are crucial for scaling TinyML beyond isolated use cases and into mainstream embedded applications worldwide.

E-ISSN: 2582-2160 • Website: www.ijfmr.com • Email: editor@ijfmr.com

#### 6.8 Summary

TinyML is a breakthrough in order to incorporate intelligence in the most limited, little devices. Due to architectural innovation, machine learning is now achievable under previously unthinkable conditions. As toolchains develop and model creation becomes more automated, TinyML is poised to take front stage in the future of ubiquitous artificial intelligence, allowing real-time insights at the very periphery.

## 7. Trade-offs, Multi-Objective Optimization, and Real-Time Processing

## 7.1 Introduction to Trade-offs in Edge AI

Deep learning models deployed on peripheral devices need for the negotiation of a complex range of tradeoffs. Edge implementations must balance a number of conflicting criteria, including resilience, energy consumption, latency, and accuracy, unlike traditional computing environments which give model performance at any computational cost first priority. Effective design of edge artificial intelligence depends on multi-objective optimisation as every application has different needs and tolerance range.

Unlike single-objective optimisation in cloud artificial intelligence (e.g., optimising accuracy), edge artificial intelligence requires techniques that can concurrently optimum several goals without sacrificing system viability. Reliable and effective artificial intelligence deployment in limited settings depends on understanding and handling of these trade-offs.

### 7.2 Key Trade-off Dimensions in Edge AI

#### 7.2.1 Accuracy vs. Efficiency

One well-known trade-off is that between resource economy and model correctness. Usually requiring deeper structures and more datasets, high-accuracy models cause higher memory consumption and computational complexity. These models become useless, nevertheless, on edge devices with limited power and computation capability unless compressed or rebuilt (Sze et al., 2017).

Pruning and quantisation, for instance, may greatly reduce model size but may cause a little accuracy loss. The application determines the degree of acceptable loss: in a recommendation system a little decline in classification accuracy might be acceptable; in medical diagnostics it is unacceptable.

#### 7.2.2 Latency vs. Throughput

Usually more crucial than throughput when a model must operate in real time is latency. Low latency models may employ smaller batch sizes, therefore reducing the computer resources needed and lowering the speed of operation.

Edge applications like motion detection or self-driving brakes have to put delay first, even if it means making models more complex or rendering the overall system less efficient (Zhao et al., 2018). Conversely, monitoring systems could be ready to cope with additional latency in return for higher output.

#### 7.2.3 Energy vs. Performance

Energy consumption is a primary constraint on mobile and embedded devices. Increasing performance through deeper networks or faster processors usually increases power draw. Therefore, energy-aware optimization—such as using lightweight models, event-driven processing, or low-power hardware accelerators—is essential (Lane et al., 2015).

Battery-powered devices like wearables or drones often require models that can operate continuously with minimal energy impact, even if this necessitates some accuracy compromise or reduced feature scope.

### 7.2.4 Memory vs. Functionality

Memory is a critical bottleneck, particularly in microcontrollers with limited RAM and flash storage.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

Developers must make choices about how much functionality to retain—such as supporting multiple tasks or sensor modalities—based on available memory. Techniques like parameter sharing, model segmentation, and dynamic memory allocation help address these constraints but involve increased development complexity.

## 7.3 Multi-Objective Optimization in Edge AI

Multi-objective optimization involves solving for **Pareto-efficient solutions**, where no one objective can be improved without worsening another. In edge AI, this typically involves navigating a **Pareto frontier** across metrics like accuracy, latency, and energy consumption.

## 7.3.1 Techniques and Algorithms

Modern techniques for multi-objective optimization are as given below:

- Evolutionary algorithms: Such as NSGA-II, which evolve populations of models toward Pareto-optimal sets based on fitness scores across multiple objectives (Deb et al., 2002).

- **Reinforcement learning**: Used in neural architecture search (NAS) to explore trade-offs dynamically during model design (Zoph et al., 2018).

- **Bayesian optimization**: Effective for searching hyperparameter spaces where evaluation is expensive by allowing prioritization of multiple metrics (Snoek et al., 2012).

- **Differentiable NAS**: Allows gradients to guide architecture search in a continuous space by jointly optimizing objectives such as accuracy (Liu et al., 2019).

These techniques are effective when integrated into **hardware-aware NAS** tools that generate models for specific device profiles.

#### 7.3.2 Model Selection Frameworks

Frameworks such as **MCUNet** (Lin et al., 2020) and **Once-for-All** (Cai et al., 2020) offer dynamic model selection depending on the deployment environment. Once-for-All trains a supernet that consist of possible sub-models search to select the best one for a given device's constraints. This enables a **deploy anywhere** approach for simplifying the deployment of AI at scale.

#### 7.4 Real-Time Processing and Adaptive Inference

Edge devices frequently operate under **non-stationary conditions**, such as fluctuating network quality, power levels, or computational load. This calls for models and systems that can **adapt at runtime** to maintain real-time responsiveness.

#### 7.4.1 Dynamic Inference Paths

It is seen that Dynamic models can adjust their execution based on input complexity or device state. For example:

- Early-exit architectures (e.g., BranchyNet) allow predictions to be made earlier in the network if confidence is high, reducing computation time for easy inputs (Teerapittayanon et al., 2016).

- Conditional computation uses gating mechanisms to skip layers or for certain inputs in order to improve energy efficiency without a full pass through the model.

#### 7.4.2 Adaptive Precision

Some systems dynamically adjust numeric precision—e.g., from 8-bit to 16-bit—based on workload intensity, leveraging **dynamic voltage and frequency scaling (DVFS)** to reduce energy consumption during low-demand periods (Horowitz, 2014).

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

### 7.4.3 Load Balancing and Scheduling

Real-time applications benefit from intelligent scheduling of model inference across devices or between edge and cloud. **Edge-cloud synergy**, as discussed in Section 5, allows load balancing under variable conditions. AI-driven schedulers and orchestration frameworks optimize task allocation based on system status, helping to maintain low-latency performance under changing conditions (Deng et al., 2020).

## 7.5 Monitoring and Feedback Loops

Monitoring plays a crucial role in enabling adaptive optimization. Real-time tracking of system metrics—such as inference time, memory usage, or thermal state—enables feedback loops that trigger reconfiguration or retraining.

Some systems integrate **lightweight profilers** or **on-device telemetry** to track performance indicators, for enabling models to flag errors when deviations occur. These adaptive mechanisms are vital for long-term deployment of edge AI in environments where reliability is critical.

#### 7.6 Research Challenges and Future Directions

Various challenges are present in optimizing across multiple objectives in real-world edge settings:

- **Uncertainty modeling**: Real-world conditions introduce uncertainty in model input and user context. Optimization algorithms must handle variability.

- Cross-platform benchmarking: Lack of standardized tools makes it difficult to evaluate models consistently across heterogeneous hardware platforms.

- **Integrated design toolchains**: Developers always work across separate toolkits for model optimization. Unified pipelines are needed to streamline the process.

- Explainability and control: Optimized models may become "black boxes," making it difficult to understand or validate trade-offs, especially in safety-critical applications.

Future work must address these issues through open benchmarks, tool unification, and cross-disciplinary research.

#### 7.7 Summary

Deep learning at the edge calls for careful balancing several competing goals, including energy cost, latency, memory use, and accuracy. By using techniques such adaptive scheduling, dynamic inference, and multi-objective optimisation, developers may build models that perform well in the face of resource restrictions. From architectural design to real-time operation, these trade-offs have to be settled not just at the model level but also all through the system lifetime. As tools and frameworks change, the creation of dependable, scalable, and sustainable edge artificial intelligence depends on our ability to properly manage these trade-offs.

#### 8. Future Directions and Challenges

## 8.1 Hardware Fragmentation and Standardization

One of the most important challenges to deep learning adoption on edge devices is hardware platform fragmentation. From limited microcontrollers to high-performance mobile GPUs, every edge environment has unique memory architectures, instruction sets, and specs. This variability complicates the implementation of a single model across devices and usually calls for platform-specific customising. This method reduces scalability (Zhang et al., 2020) and raises development's expense.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

To remedy this, future studies have to focus on the creation of hardware-agnostic optimisation frameworks and interoperable toolchains. Emerging technologies representing advancement towards platform-independent model deployment include ONNX (Open Neural Network Exchange) and TVM (Tensor Virtual Machine). Still, these ideas have to be further standardised and included into business processes. Additionally, there is a growing need for **benchmarking suites** that can evaluate edge AI models across devices using standardized datasets, metrics (latency, energy, accuracy), and profiling tools. Initiatives such as **MLPerf Tiny** are working to fill this gap, but broader adoption is still required to ensure fair and reproducible evaluations.

## 8.2 On-Device Training and Lifelong Learning

Most edge AI deployments today focus solely on inference. However, **on-device training** and **lifelong learning** represent critical next steps, particularly for applications that involve personalized or continuously evolving data, such as wearable health monitors or smart home assistants (Parisi et al., 2019). On-device training presents several challenges, including:

- Limited compute and memory resources

- Energy constraints

- Non-IID and noisy data

- Lack of secure storage and logging

Innovations such as **few-shot learning**, **federated continual learning**, and **efficient backpropagation techniques** tailored for constrained devices may enable more adaptable and personalized AI systems. Future research will need to balance adaptability with security and performance guarantees.

#### 8.3 Trust, Privacy, and Security

As edge AI moves closer to the user—into personal devices, vehicles, and homes—issues of **data privacy**, **model robustness**, **and security** become paramount. Federated learning and TinyML already address aspects of privacy by keeping raw data local, but other vulnerabilities remain:

- Model inversion attacks can reconstruct training data from model outputs.

- Adversarial examples can mislead edge models with small, crafted perturbations.

- Model extraction can allow attackers to clone proprietary models through repeated querying.

Developing **privacy-preserving machine learning** techniques—such as differential privacy, homomorphic encryption, and secure multi-party computation—remains a major area of interest (Bonawitz et al., 2019). At the same time, ensuring robustness against adversarial attacks without increasing model complexity is an ongoing challenge, particularly under the strict constraints of edge environments.

#### 8.4 Dynamic and Context-Aware AI

Edge devices often operate in **non-stationary environments**, where resource availability, network quality, and user behavior vary over time. This variability calls for **context-aware and self-adaptive models** that can adjust their behavior dynamically.

Already under research are methods like runtime profiling, dynamic model scaling, and context-aware scheduling. These systems sometimes, however, depend on complex coordination among hardware, OS-level schedulers, and artificial intelligence frameworks. Future advancements will have to close this gap so that artificial intelligence models may be autonomously adapted in practical edge environments.

#### 8.5 Green AI and Sustainability

Growing prevalence of artificial intelligence at the edge also begs questions about sustainability and energy consumption. Although edge devices are usually more efficient than cloud-based solutions, the

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

expanding scope of edge artificial intelligence begs long-term environmental concerns.

New studies in Green AI support assessing models not only in performance but also in their energy and carbon footprints (Schwartz et al., 2020). Standard benchmarks for energy-efficient artificial intelligence might eventually become operations per Joule and energy-delay product (EDP). Scalable and environmentally friendly edge AI solutions depend on include these factors throughout model creation and deployment.

## 8.6 Toward Unified Edge AI Frameworks

The evolution of peripheral artificial intelligence is marked by scattered processes including different technologies for training, compression, deployment, and runtime monitoring. For many companies and developers, this complexity is a hurdle.

Demand for end-to- end peripheral artificial intelligence systems that abstract this complexity while preserving adaptability and control is growing. These venues should help:

- Seamless integration of compression techniques

- Hardware-aware deployment

- Support for real-time monitoring and feedback

- Adaptive model updates

Open-source initiatives, industry consortia, and collaborative research efforts will play a pivotal role in advancing these unified platforms, democratizing access to edge AI technologies.

#### 8.7 Summary

As edge AI continues to mature, the field faces several critical challenges that span across technical, ethical, and environmental domains. Addressing hardware fragmentation, enabling on-device learning, strengthening security, and fostering adaptability are all essential to the next generation of intelligent edge systems. Moreover, building sustainable and unified AI deployment pipelines will be key to scaling edge AI globally.

The future of edge AI lies not just in more efficient models, but in **context-aware**, **secure**, **personalized**, **and energy-conscious systems** that can operate autonomously in a wide range of real-world scenarios. Tackling these challenges will require interdisciplinary collaboration, standardized benchmarks, and robust toolchains that bridge research and application.

#### 9. Conclusion

The combination of artificial intelligence and edge computing has enabled real-time, intelligent decision-making in very limited areas feasible and creates transforming opportunities across sectors. Still, the implementation of deep learning models on peripheral devices is marked by a range of difficult problems including restricted processing capability, memory limits, and energy budgets. The most current optimisation methods meant to solve the performance gap between conventional deep models and the pragmatic limitations of edge technology have been assembled in this review.

Built on basic ideas such pruning, quantisation, information distillation, and lightweight architectural design, is effective edge artificial intelligence. Emerging fields of TinyML, federated learning, edge-cloud cooperation, and hardware-aware approaches are gradually supporting them. Customised model designs that successfully balance the trade-offs between energy, memory, latency, and accuracy have also been made possible by the evolution of multi-objective optimisation and neural architecture search. These developments taken together allow intelligent models to be executed on a range of devices, including cellphones and microcontrollers.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

As edge artificial intelligence gains broad acceptance, the field faces some ongoing challenges, nevertheless. More critical than ever is the need for safe, privacy-preserving learning systems; hardware fragmentation makes deployment more difficult. Furthermore, a constant innovation is required in hardware and software co-design to allow sustainability, on-device learning as well as real-time adaption. Future research has to give ethical deployment, explainability, and robustness a priority along with performance and efficiency.

The creation of effective deep learning for peripheral devices is a multidisciplinary effort in the final analysis that calls for the cooperation of machine learning researchers, embedded systems architects, and application developers. As the ecosystem develops, it is essential to provide consistent frameworks and easily available toolchains supporting scalable, safe, and sustainable artificial intelligence. The author may release fresh degrees of responsiveness, autonomy, and social value throughout a broad range of real-world applications by keeping the intelligence of current AI while optimising for the limits of the edge.

#### References

- 1. Arivazhagan, M., Aggarwal, V., Singh, A. K., & Choudhary, S. (2019). Federated learning with personalization layers. arXiv preprint arXiv:1912.00818.

- 2. Banbury, C., Reddi, V., Torelli, P., et al. (2021). MLPerf Tiny Benchmark. arXiv preprint arXiv:2106.07597.

- 3. Blanchard, P., El Mhamdi, E. M., Guerraoui, R., & Stainer, J. (2017). Machine learning with adversaries: Byzantine tolerant gradient descent. Advances in Neural Information Processing Systems, 30.

- 4. Bonawitz, K., Eichner, H., Grieskamp, W., et al. (2019). Towards federated learning at scale: System design. Proceedings of the 2nd SysML Conference.

- 6. Cai, H., Gan, C., Wang, T., Zhang, Z., & Han, S. (2019). Once-for-all: Train one network and specialize it for efficient deployment. arXiv preprint arXiv:1908.09791.

- 7. Careem, R., Johar, G., & Khatibi, A. (2024). Deep neural networks optimization for resource-constrained environments: techniques and models. Indonesian Journal of Electrical Engineering and Computer Science, 33(3), 1843-1854.

- 8. Chen, J., & Ran, X. (2019). Deep learning with edge computing: A review. Proceedings of the IEEE, 107(8), 1655–1674.

- 9. Chen, Y., Emer, J., & Sze, V. (2019). Eyeriss: A spatial architecture for energy-efficient dataflow for convolutional neural networks. IEEE Micro, 37(3), 12–21.

- 10. Chen, Y., Moreau, T., Jiang, Z., et al. (2018). TVM: An automated end-to-end optimizing compiler for deep learning. 13th USENIX Symposium on Operating Systems Design and Implementation (OSDI 18), 578–594.

- 11. Cheng, Y., Wang, D., Zhou, P., & Zhang, T. (2020). Model compression and acceleration for deep neural networks: The principles, progress, and challenges. IEEE Signal Processing Magazine, 37(6), 101–112.

- 12. Deng, S., Zhao, H., Fang, B., Yin, J., Dustdar, S., & Zomaya, A. Y. (2020). Edge intelligence: The confluence of edge computing and artificial intelligence. IEEE Internet of Things Journal, 7(8), 7457–7469.

- 13. Esser, S. K., Appuswamy, R., Merolla, P., Arthur, J. V., & Modha, D. S. (2016). Backpropagation for energy-efficient neuromorphic computing. Advances in Neural Information Processing Systems, 29.

E-ISSN: 2582-2160 • Website: <a href="www.ijfmr.com">www.ijfmr.com</a> • Email: editor@ijfmr.com

- 14. Esser, S. K., McKinstry, J. L., Bablani, D., Appuswamy, R., & Modha, D. S. (2020). Learned step size quantization. International Conference on Learning Representations (ICLR).

- 15. Farooq, M., & Khan, M. H. (2024). Edelear: Edge-based deep learning with resource awareness for efficient model training and inference for iot and edge devices. International Journal of Scientific Research in Network Security and Communication, 12(1), 1-8.

- 16. Gadepalli, K., Li, T. S. L., Wang, S., et al. (2021). A full-stack open-source machine learning infrastructure for the RISC-V ecosystem. arXiv preprint arXiv:2105.04649.

- 17. Gou, J., Yu, B., Maybank, S. J., & Tao, D. (2021). Knowledge distillation: A survey. International Journal of Computer Vision, 129(6), 1789–1819.

- 18. Gutierrez-Torre, A., Bahadori, K., Iqbal, W., Vardanega, T., Berral, J. L., & Carrera, D. (2021). Automatic distributed deep learning using resource-constrained edge devices. IEEE Internet of Things Journal, 9(16), 15018-15029.

- 19. Han, S., Pool, J., Tran, J., & Dally, W. J. (2015). Learning both weights and connections for efficient neural networks. Advances in Neural Information Processing Systems, 28.

- 20. Hard, A., Rao, K., Mathews, R., et al. (2018). Federated learning for mobile keyboard prediction. arXiv preprint arXiv:1811.03604.

- 21. Hinton, G., Vinyals, O., & Dean, J. (2015). Distilling the knowledge in a neural network. arXiv preprint arXiv:1503.02531.

- 22. Horowitz, M. (2014). 1.1 Computing's energy problem (and what we can do about it). 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 10–14.

- 23. Howard, A. G., Zhu, M., Chen, B., et al. (2017). MobileNets: Efficient convolutional neural networks for mobile vision applications. arXiv preprint arXiv:1704.04861.